DDR内存原理 - 2

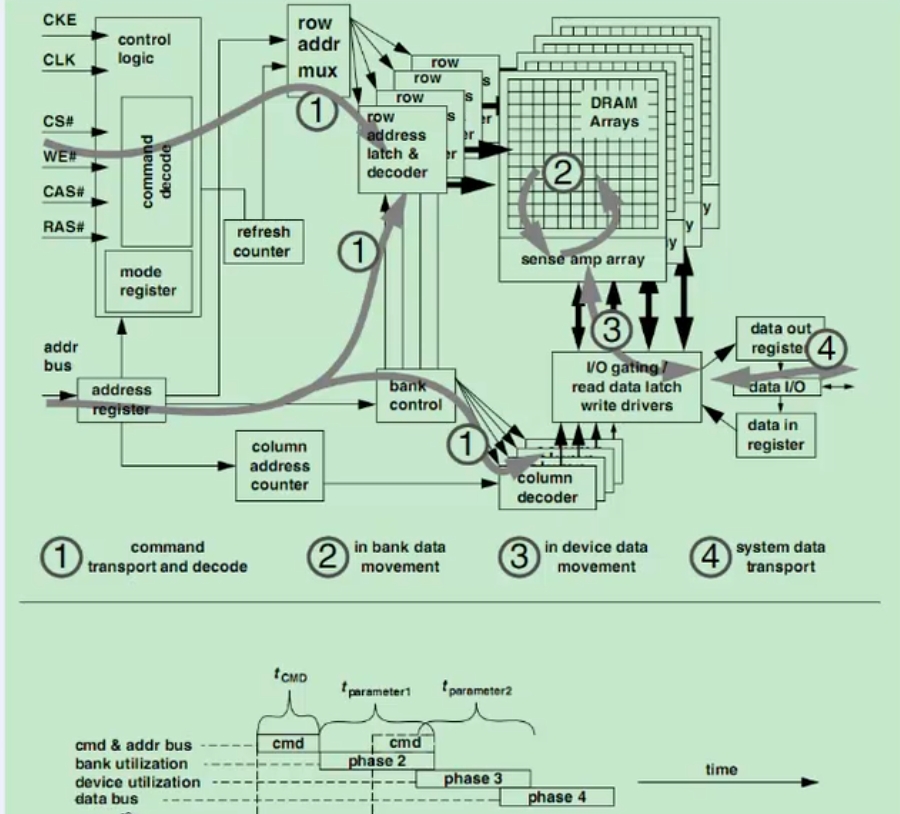

四阶段分析

Top View:

一阶段 - 命令阶段 - command transport and decode

在这个阶段,Host 端会通过 Command Bus 和 Address Bus 将具体的 Command 以及相应参数传递给 DRAM。DRAM 接收并解析 Command,接着驱动内部模块进行相应的操作。其中会根据将addr bus上的数据解码成对应的row address和通过bank control解码后得到对应的bank,其次对应的column也会解码得到对应的地址

二阶段 - bank应用 - in bank data movement

在这个阶段,第一阶段发送需要读取的 Column 的地址给 DRAM。然后 DRAM 再将 Active Command 所选中的 Row 中,DRAM 就将 Memory Array 中的数据从 DRAM Cells 中读出到 Sense Amplifiers,或者将数据从 Sense Amplifiers 写入到 DRAM Cells。

三阶段 - device应用 - in device data movement

这个阶段中,数据将通过 IO 电路缓存到 Read Latchs 或者通过 IO 电路和 Write Drivers 更新到 Sense Amplifiers。

四阶段 - 数据总线 - system data transport

在这个阶段,进行读数据操作时,SDRAM 会将数据输出到数据总线上,进行写数据操作时,则是 Host 端的 Controller 将数据输出到总线上。

在上述的四个阶段中,每个阶段都会有一定的耗时,例如数据从 DRAM Cells 搬运到 Read Latchs 的操作需要一定的时间,因此在一个具体的操作需要按照一定时序进行。同时,由于内部的一些部件可能会被多个操作使用,例如读数据和写数据都需要用到部分 IO 电路,因此多个不同的操作通常不能同时进行,也需要遵守一定的时序。此外,某些操作会消耗很大的电流,为了满足 SDRAM 设计上的功耗指标,可能会限制某一些操作的执行频率。

这四个阶段都有一个txxx类的命名,这都是在ddr init过程中要去配置的。2阶段和3阶段里参数比较多。

Memory Array内部结构

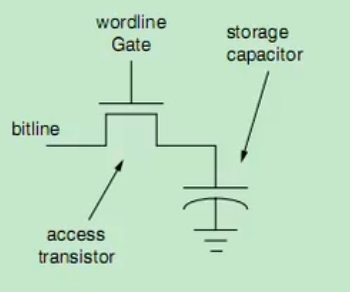

下图在前面的章节也见识过,它是一个bit的存储单元。

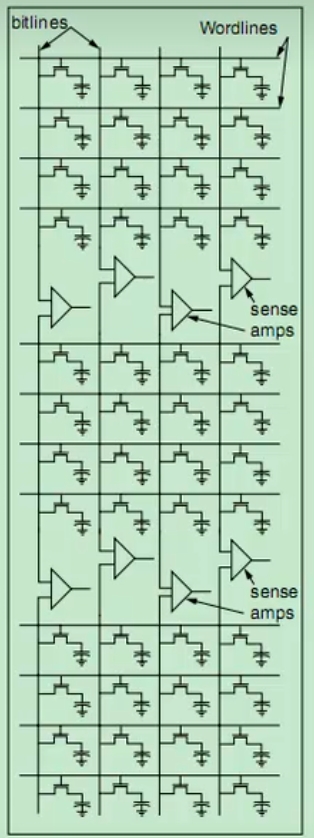

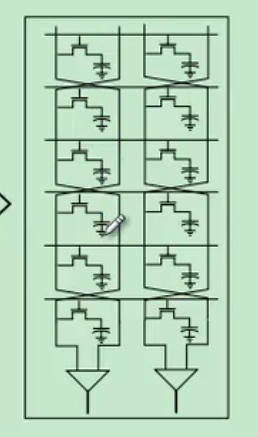

下图则是由上图的存储单元,组成的一个阵列:

由于电容信号,非常微弱,每一次将数据送往bitline线,还不足以将bitline的点位升高很多。

所以这个阵列需要一个预充电的动作(precharge)。precharge需要将bitline的电平设置为Vcc/2

当wordline打开的时候,数据经过bitline下来,会将Vcc/2抬高一丢丢,微弱上升到Vcc*2/3或者更多(如果是写0就是微弱下降一丢丢),这才能让电容完全充满或者清空。

bitline整根线也存在寄生电容,单一的bit存储单元使用的电容与其相比算是很小的了。小电容无法将大电容一次性充电到vcc。sanse电路可以感知到这个微弱的变化。

上图中还存在多个sense amps,是因为这个阵列共有16K个行,其电容是非常大了,所以还需要将这16k的行分成若干个单元,比如说每64个row sense一下,这就造成每隔一段row就有一些sense存在。

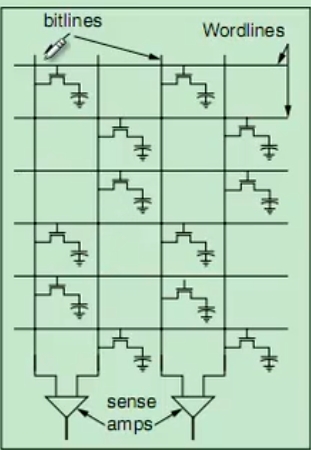

这种电路在早期位密度较低时适用,现在使用的则是下面的差分结构:

同一根bitline,使用两根线表示(分别记为+/-)。数据存储位被平均的放在这两根线上。在precharge阶段,这两根线都保持在Vcc/2左右,一旦wordline选通,+bitline会上升到vcc,而-bitline下降到0,这样一来sense amps对电平变化的感知灵敏度就更高。将sense电路结构复杂度降低。

两根超长的line,电容是非常大的,所以后期又出现了这种双绞电路:

下面着重分析双绞电路中其中一列的结构,工作原理,时序

双绞电路

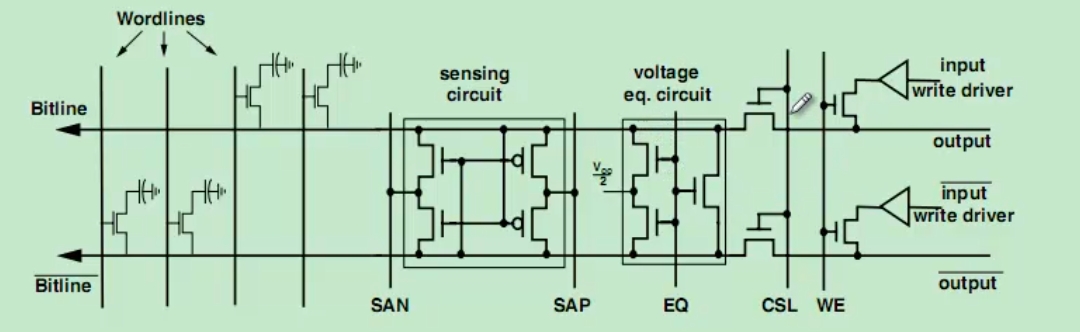

这是双绞电路的一个抽象表示,实际电路会更加复杂:

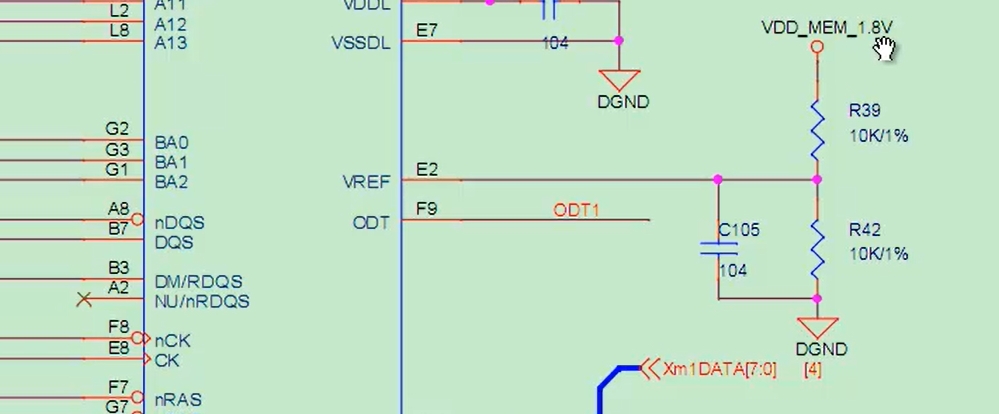

voltage eq. circuit就是预充电电路(precharge), 它的功能就是将bitline上的电平设置到Vcc/2。它有一根EQ线,属于device内部的控制线。

DMC向device发送precharge命令后,device内部的EQ控制线会被打开,三个场效应管都会导通。Vcc/2的电压来自外部输入Vref,从而两条bitline上都有了Vcc/2的预充电电压。

precharge结束后是数据读取阶段。wordlines选通,其上的电容释放出微弱电压。bitline上的电压略微上升一点点( > Vcc/2)。

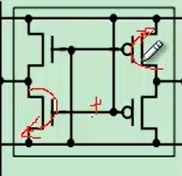

sensing circuit感知到电压的微弱上升,SAN(Vcc/2) == SAP(Vcc/2)的平衡,红色标记下的两个场效应管导电性越来越好,其余两个越来越差,一段时间以后,bitline上升到Vref,bitline反则降到0。

接下来就是I/O阶段,就是将1/0信号送出去,承担此任务的是右边的CSL,即column select line上的两个场效应管,将列选择线选通后,这两个场效应管就导通,那么1/0信号也就输出。

最后,是restore阶段,bitline上的高电平会反向对wordline上的电容进行充电,即数据回写。

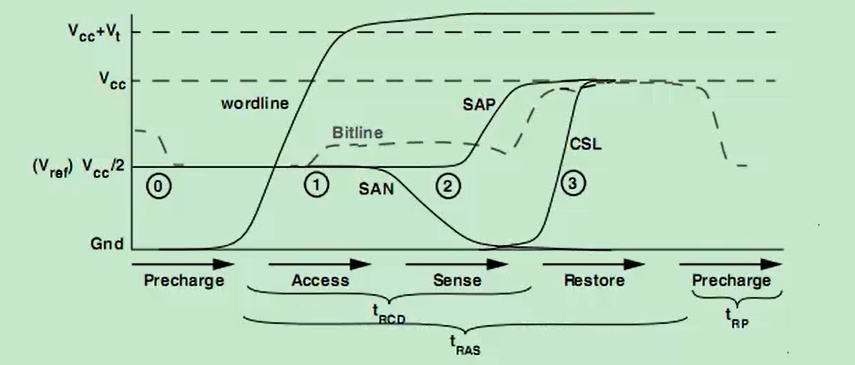

各阶段 - 电平与时序的关系

对上图的时序分析:

0处的电平也就是一个memory array里某个电容的电平值。wordline一开始并未选中,但precharge电路不受影响,会给bitline充电到Vcc/2。这是precharge阶段

由于DMC的某个命令,wordline被选中,电平逐渐上升到Vcc。

进入到阶段1,开始对bank进行访问。bitline被选中,开始对目标存储cell电容进行充电,bitline开始逐渐上升。这是access阶段

bitline的微弱上升,导致sensing circuit的平衡被打破,SAP上的电压向上抬高,SAN的电压降低。这就是sense阶段

access阶段和sense阶段被合称RCD阶段,tRCD也就表示这一阶段的是时间。

SAP上的电压向上抬高,SAN的电压降低的同时,bitline也在慢慢升高,在第二阶段结束时,bitline维持在高电平。CSL被选通,也就是第三阶段CSL先逐步抬高。信号被输出。

restore阶段,输出的高电平,反向充回存储cell。bitline回到Vcc/2。

术语解析:

RCD全称为Row to Column Delay. 这是指Row被打开,到Column被选中,之间的延迟。这是一个非常关键的参数。

RAS全称为Row Access Strobe。指从row地址被解码后,wordline被选中,到整个数据输出,并且restore保存进去为止。

RP全称为Row precharge

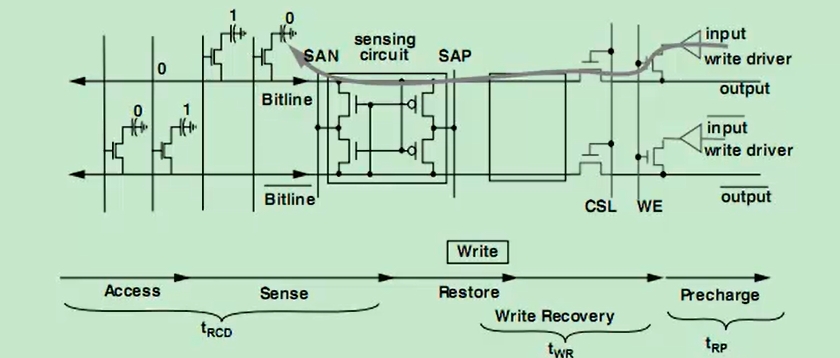

向存储cell写1:

写入时序与读取时序略有不同

wr全称为write recovery

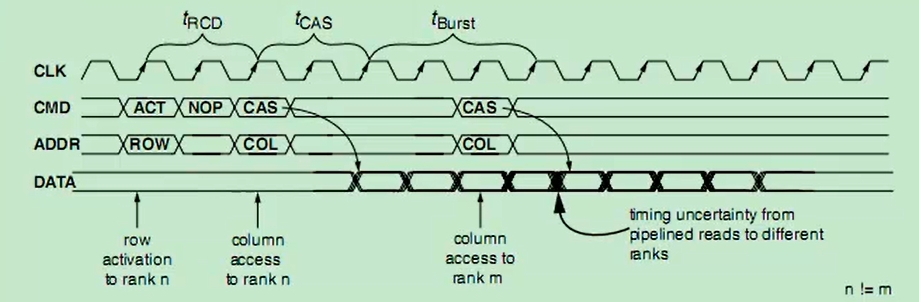

加入CLK信号后的正式时序图

SDRAM

CAS:column access strobe latency,也称为CL,column letency.

burst len = 4

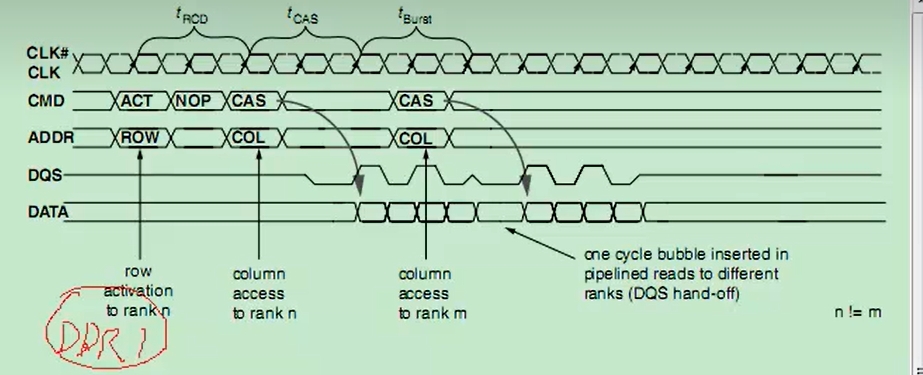

DDR1

与SDRAM的时序很相似,CLK双边沿都会采样。