Linux内核中断子系统0 - 综述

本系列文章列表

- GIC控制器讲解

- GIC控制器驱动分析

- 级联中断控制器的原理与驱动实现

- 中断子系统综述

- ARM中断过程

- irq domain

- IRQ Number和irq_desc

- high level irq event handler

- 内核驱动中断相关的API

- softirq

- tasklet

中断子系统涉及到四大部分:

- Linux内核通用中断处理模块。这部分是硬件无关的无论是哪种CPU,哪种controller,其中断处理的过程都有一些相同的内容,这些相同的内容被抽象出来,和HW无关。此外,各个外设的驱动代码中,也希望能用一个统一的接口实现irq相关的管理(不和具体的中断硬件系统以及CPU体系结构相关)这些“通用”的代码组成了linux kernel interrupt subsystem的核心部分。

- CPU Arch SPEC的中断处理。中断控制器分配中断到不同的CPU,CPU进行处理,不同架构的CPU这部分中断处理的代码有差异

- Interrupt controller驱动代码。不同系统使用的中断控制器不同,如APIC,GIC等,差异也比较大。

- 普通外设驱动。外设驱动通过调用 Linux内核通用中断处理模块 中的通用API来做驱动开发,如注册中断号以及中断回调。

中断的硬件系统:

中断硬件系统主要有三种器件参与,各个外设、中断控制器和CPU。各个外设提供irq request line,在发生中断事件的时候,通过irq request line上的电气信号向CPU系统请求处理。外设的irq request line太多,CPU需要一个小伙伴帮他,这就是Interrupt controller。Interrupt Controller是连接外设中断系统和CPU系统的桥梁。根据外设irq request line的多少,Interrupt Controller可以级联。CPU的主要功能是运算,因此CPU并不处理中断优先级,那是Interrupt controller的事情。对于CPU而言,一般有两种中断请求,例如:对于ARM,是IRQ和FIQ信号线,分别让ARM进入IRQ mode和FIQ mode。对于X86,有可屏蔽中断和不可屏蔽中断。

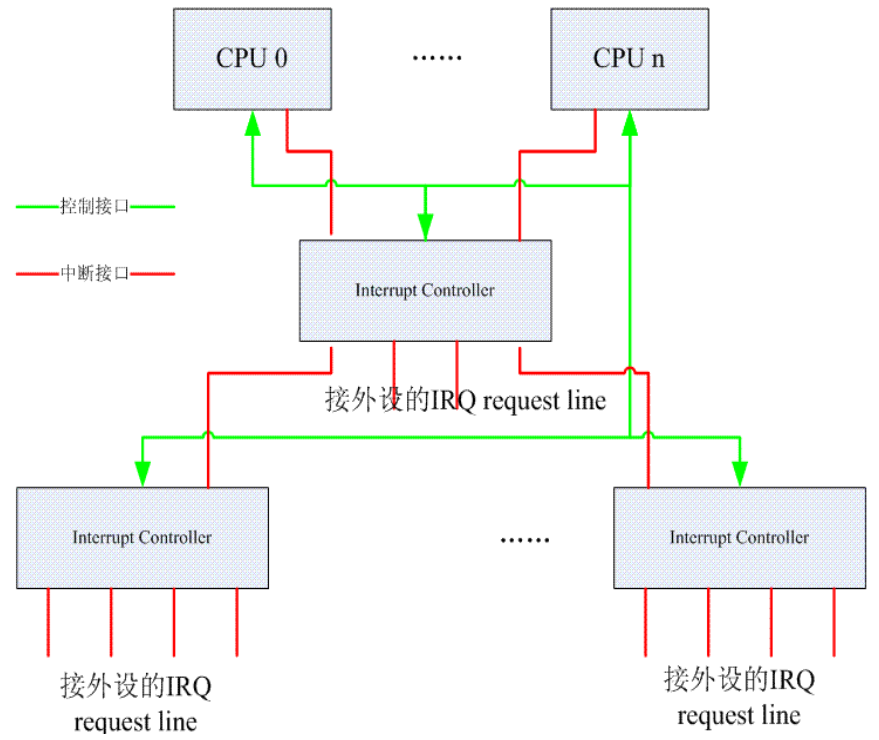

中断系统的逻辑Block图

系统中有若干个CPU block用来接收中断事件并进行处理,若干个Interrupt controller形成树状的结构,汇集系统中所有外设的irq request line,并将中断事件分发给某一个CPU block进行处理。

从接口层面看,主要有两类接口:

- 一种是中断接口。有的实现中,具体中断接口的形态就是一个硬件的信号线,通过电平信号传递中断事件(ARM以及GIC组成的中断系统就是这么设计的)。有些系统采用了其他的方法来传递中断事件,比如x86+APIC(Advanced Programmable Interrupt Controller)组成的系统,每个x86的核有一个Local APIC,这些Local APIC们通过ICC(Interrupt Controller Communication)bus连接到IO APIC上。IO APIC收集各个外设的中断,并翻译成总线上的message,传递给某个CPU上的Local APIC。因此,上面的红色线条也是逻辑层面的中断信号,可能是实际的PCB上的铜线(或者SOC内部的铜线),也可能是一个message而已。

- 另一种是控制接口。CPU和Interrupt Controller之间还需要有控制信息的交流。Interrupt Controller会开放一些寄存器让CPU访问、控制。